FPGA 與 Verilog 之基礎與FPG.

帶領學員理解Verilog的實作方法,以及廣泛利用實例引領學員利用FPGA來實作

FPGA 與 Verilog 之基礎與FPGA自走車實作

課程型態/ 實體

上課地址/ 工研院新竹光復院區-1館

時數/ 18小時

起迄日期/ 2024/05/31~2024/06/07

聯絡資訊/ 劉懿萱 03-5743729

報名截止日/ 2024/05/23

---------------------------------------

課程介紹FPGA是一種可編程的數位邏輯晶片,屬於ASIC領域中一種半定製電路,FPGA的發展不但解決了定製電路不足,並且能夠克服可編程器電路數有限的問題,再加上FPGA自身具有的設計周期短、開發成本低和設計靈活等特點,使得FPGA的開發越來越流行,為進入IC設計必經學習之路。 本課程帶領學員理解Verilog的實作方法,以及廣泛利用實例引領學員利用FPGA來實作Verilog程式。本課程將會從Verilog程式語言之基礎開始,引領學員熟悉Verilog的各種語法,包含Combinational Circuits、Sequential Circuits、Finite State Machine、以及進階的Verilog語言之編寫方式,帶領學員使用正確的觀念,來撰寫Verilog程式,並將程式實作於Xilinx FPGA開發板上。本課程重視基礎與實作之結合,在課程中除了引領學員們理解硬體程式設計之流程概念外,各個課題亦包含FPGA之實作訓練。在課程的最後,將帶領學員們使用FPGA結合自走車,利用紅外線和超音波等感測裝置,進行FPGA小車於賽道上之循跡及避障任務。 課程目標Ø 帶領學員們學習Verilog之基礎知識 Ø 指導學員們熟悉正確之Verilog撰寫觀念及技巧 Ø 說明FPGA以及硬體設計流程:從架構發想到實體設計 Ø 指導學員們熟悉將Verilog實作至FPGA之流程 Ø 帶領學員們進行Verilog與FPGA之各項實作訓練,最終完成FPGA自走小車之實作 Ø 提升學員之數位邏輯的思維、並行設計的理念、資源的合理利用、及系統與模組設計能力 課程特色Ø 徹底掌握,除了強調Verilog之語法撰寫,亦將說明各種不同語法於實際合成電路時之差異。 Ø 手把手實戰,本課程包含各項FPGA之實作訓練。 Ø 學員手把手實作FPGA自走小車,有機會將作品實際驗證於循跡及避障任務上。 適合對象Ø 有意從事PLD、CPLD、FPGA、IC相關研發工作者。 Ø 資訊、資工、資管、電子、電機等相關科系畢業生。 Ø 熟悉邏輯設計及計算機架構者佳。 講師簡介李老師 【學歷】 Ÿ 美國普林斯頓大學電機工程博士 Ÿ 國立台灣大學電子工程學研究所碩士 Ÿ 國立台灣大學電機工程學系學士 【專業領域】 Ÿ 智慧型機器人 Ÿ 深度增強式學習 Ÿ 電腦視覺 Ÿ 平行程式與系統設計 Ÿ 多核心處理器系統設計 課程大綱

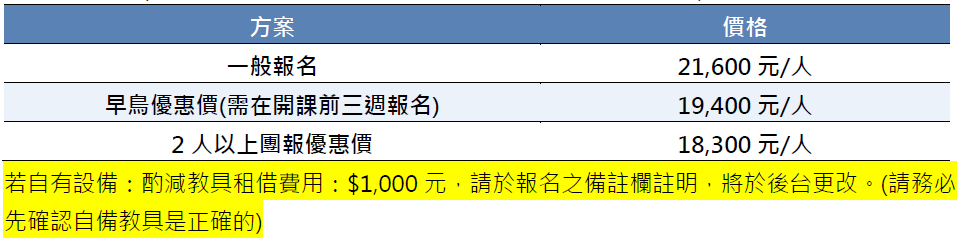

課程費用◆ 本課程歡迎企業包班,請來電洽詢 課程承辦人劉小姐(Ivy) 03-5743729。 ◆ 團報 3 人以上,請來信課程承辦人itri537622@itri.org.tw,將為您提供企業團報優惠價。

注意事項1. 為確保您的上課權益,報名後若未收到任何回覆,敬請來電洽詢方完成報名。 2. 因課前教材、講義及餐點之準備及需為您進行退款相關事宜,若您不克前來,請於開課三日前告知,以利行政作業進行並共同愛護資源。 3. 若原報名者因故不克參加,但欲更換他人參加,敬請於開課前二日通知。 4. 教具FPGA自走車係為租用,若需持有,請告知以學員另行向供應商直接購買。 附件 |

.jpg&ext=_PosterPic)